英特尔的下一代 PC 处理器,性能据说会有 50% 的提升。

本周五,英特尔揭幕了即将推出的基于全新 18A 节点的 Panther Lake 芯片的最新信息。英特尔表示,这些芯片在功耗与 Lunar Lake 一代相当的情况下,性能大幅提升,或在多线程任务中功耗比 Arrow Lake-H 处理器降低 30%。

根据以往的发布周期,我们很可能会在 2026 年初的 CES 上听到更多关于这些芯片的消息。英特尔表示,这些芯片将于 2026 年 1 月开始大量上市。

在 AMD、高通芯片不断冲击个人电脑市场市场份额的情况下,英特尔希望通过新一代产品 CPU、GPU、AI 性能的全面增强,以及续航能力方面的提升来全面提升竞争力。

在 Panther Lake 上,英特尔考虑了更多可扩展性,希望进一步提升整个 SoC 的利用率。

Panther Lake 这代 SoC 均采用相同的先进 P 核心、E 核心和 iGPU 架构,同时为笔记本制造商提供了更大的自由度,可以根据更广泛的买家和价位定制产品。作为英特尔首款搭载基于最新 18A 工艺节点制造的计算模块的产品,Panther Lake 的设计与性能表现尤为引人关注。

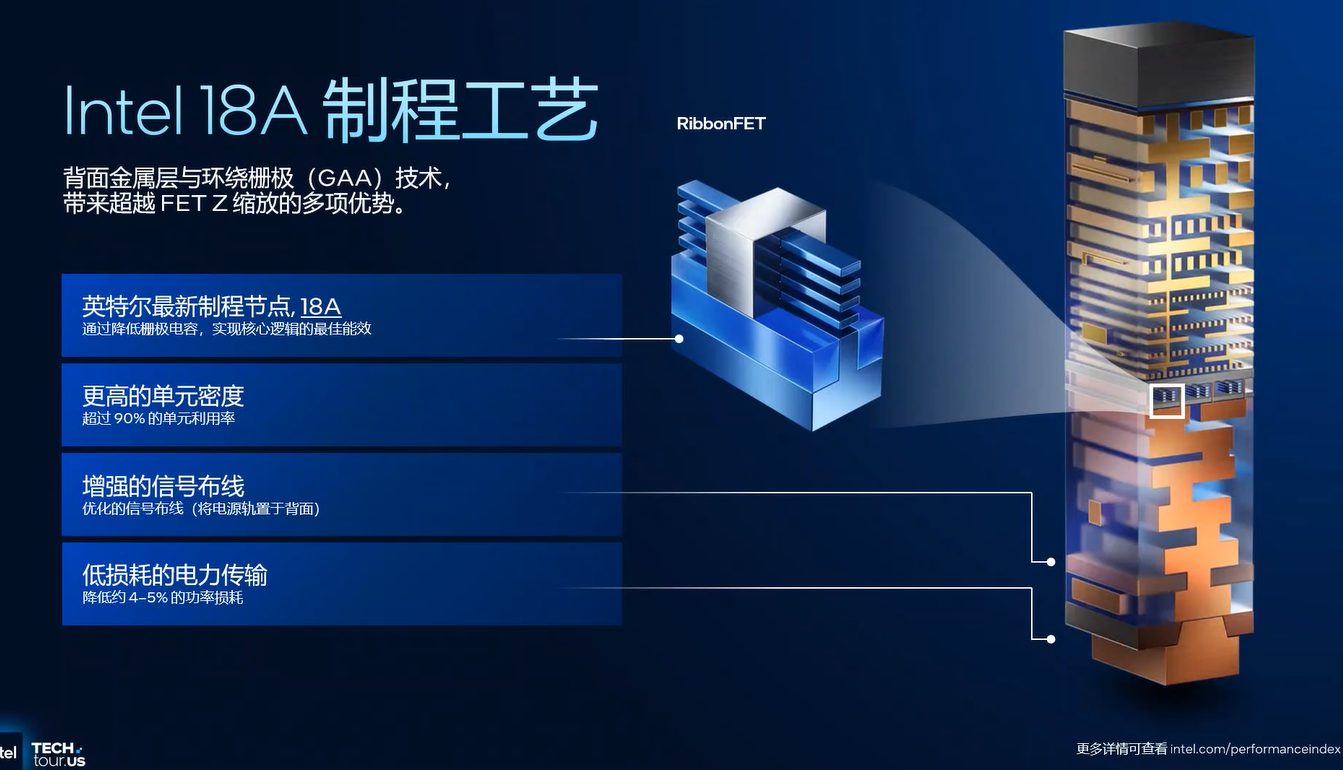

Panther Lake 的计算模块是首批基于英特尔尖端 18A 节点(等效 2nm)制造的产品之一,因此工艺制程得到了重点介绍。18A 是英特尔(也可能是业界)首个采用两项重大创新的大批量生产工艺,旨在实现未来的扩展和能效提升:全栅环 (GAA) 晶体管(英特尔称之为 RibbonFET)和背面供电网络(英特尔称之为 PowerVia)。

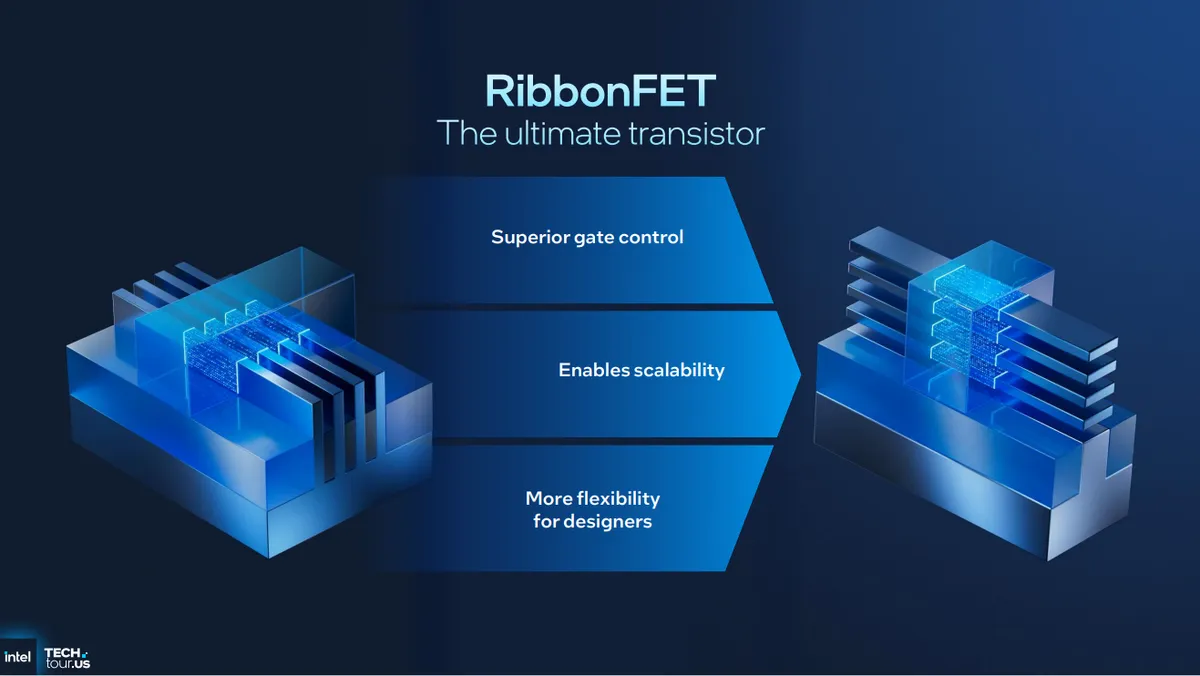

英特尔将其 RibbonFET 描述为 “终极晶体管”,因为其栅极结构实现了对 channel 的 “完全控制”。与 FinFET 相比,RibbonFET 的栅极结构没有延伸到 channel 底部,因此在控制漏电流方面存在 “弱点”,而 RibbonFET 的栅极结构则完全包裹了 channel(由器件核心的硅纳米片堆栈定义),从而最大限度地减少了晶体管关闭时产生的不良漏电流。在其他重要特性中,更低的漏电流意味着芯片运行时能量的浪费更少。

英特尔还表示,RibbonFET 对设计人员来说比 FinFET 更加灵活。RibbonFET 的数量及其宽度均可调整,从而根据特定单元的需求定制晶体管的性能特征。

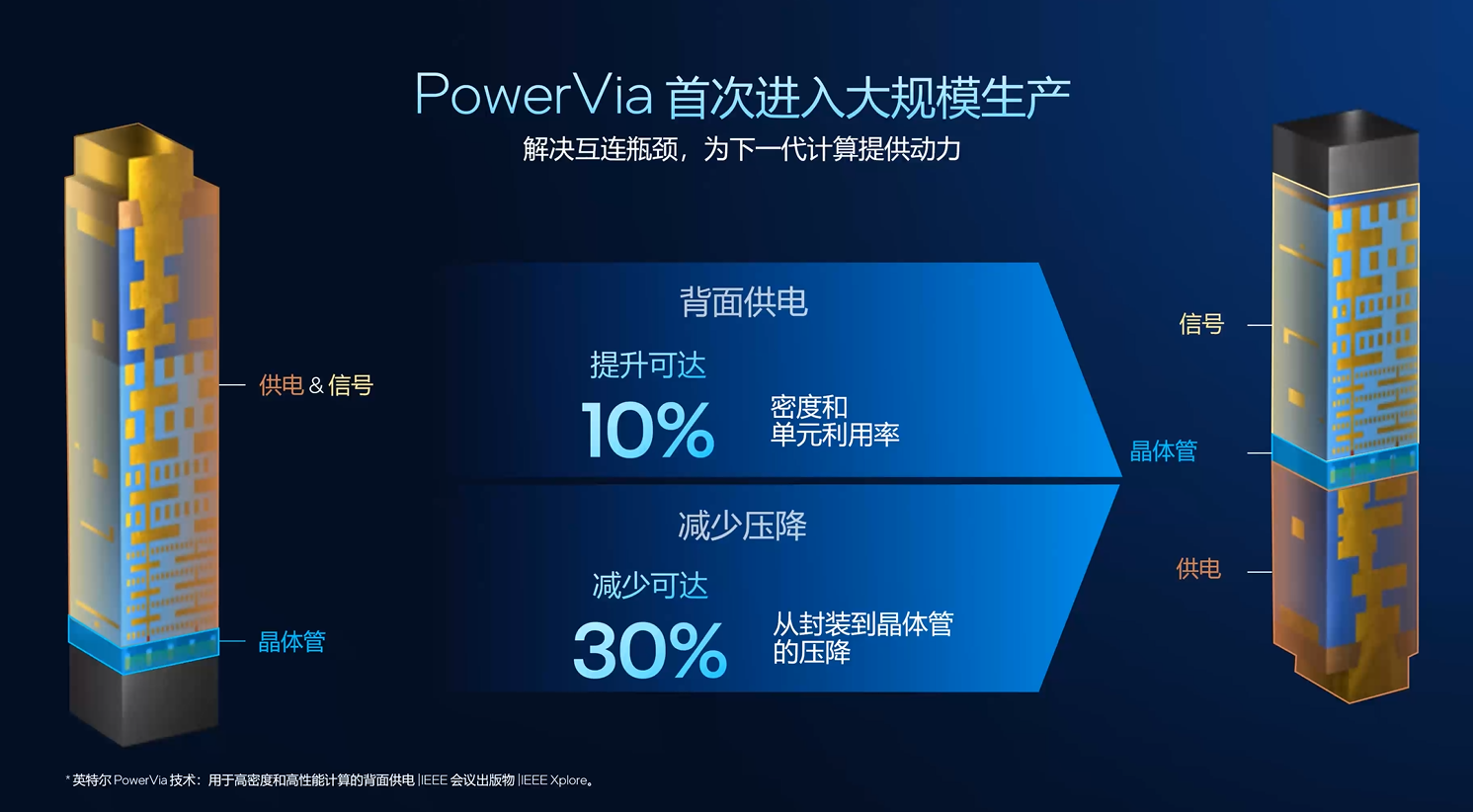

PowerVia 是英特尔推出的背面供电网络 (backside power delivery network) 技术,它为芯片制造带来了第二种创新方法。随着硅片工艺的密度越来越高,在晶体管上方高效布线信号线和电源线变得越来越具有挑战性,因为这些线路会争夺越来越宝贵的空间。

背面供电方法并非在晶体管上方同时构建电源线和信号线,而是首先在晶圆正面创建晶体管和信号线。在下一个生产步骤中,晶圆被翻转,背面被抛光,直到晶体管触点露出。然后将供电金属层直接连接到晶体管。

英特尔表示,PowerVia 可将晶圆正面的密度提高 10%,并简化布线。在电力传输方面,背面金属层可将从封装到晶体管的功率损耗降低 30%。

总而言之,18A 技术在功耗与英特尔 3 相同的情况下,频率提升 15%,密度相比相同工艺提升 1.3 倍。设计人员还可以利用 18A 的先进技术,在性能与英特尔 3 相同的情况下,让芯片的功耗降低 25%。

在新制程之上,Panther Lake 上的 Cougar Cove P 核心又进行了一些优化,它采用了 “基于人工智能” 的电源管理方法,可根据不同工作负载的需求动态调整某些功能单元(如预取器)的积极性,以提升效率。

Darkmont E-core 的改进则更多,除了同样的动态调整机制之外,Darkmont 也提升了分支预测的准确性。它还通过采用循环流检测技术来节省前端功耗,该技术允许芯片前端在某些指令序列执行期间关闭电源。Darkmont 还扩展了芯片使用纳码序列执行复杂指令的情况,这些指令传统上由 x86 CPU 的微码引擎处理。

当然,并非 Panther Lake SoC 的每个部分都使用了 18A 制程。英特尔采用与 Meteor Lake 相同的 “分解式架构” 概念,这种方法将 SoC 的不同功能单元分成单独制造的 “tile”,这些 tile 在英特尔自己的晶圆厂或台积电等代工厂生产,然后使用英特尔的 Foveros 封装技术将它们连接在一起。

但每个 Panther Lake 计算模块都在英特尔自家的晶圆厂使用 18A 制造,其由三个基本核心复合体构成。到目前为止,一个计算模块最多可以包含四个 Cougar Cove P 核心、八个 Darkmont E 核心,以及一个由另外四个 Darkmont E 核心组成的单独 “低功耗岛” 集群,这些 “低功耗岛” 旨在将合适的工作负载 “限制” 到低功耗计算域,以延长电池寿命。

18A 计算块还包括英特尔第五代 NPU、用于笔记本电脑高级网络摄像头的第七代图像处理单元 (IPU) 以及与图形块分离的 Xe 媒体和显示引擎。

英特尔在 Xe3 集成显卡配置了类似于英伟达 DLSS 的插帧技术,多帧生成每一帧最多可额外生成 3 个合成帧,此外之前支持 XeSS2 帧生成的都可以直接提供多帧生成,同时搭配 Xe LL 低延迟、Xe SS 超分技术。

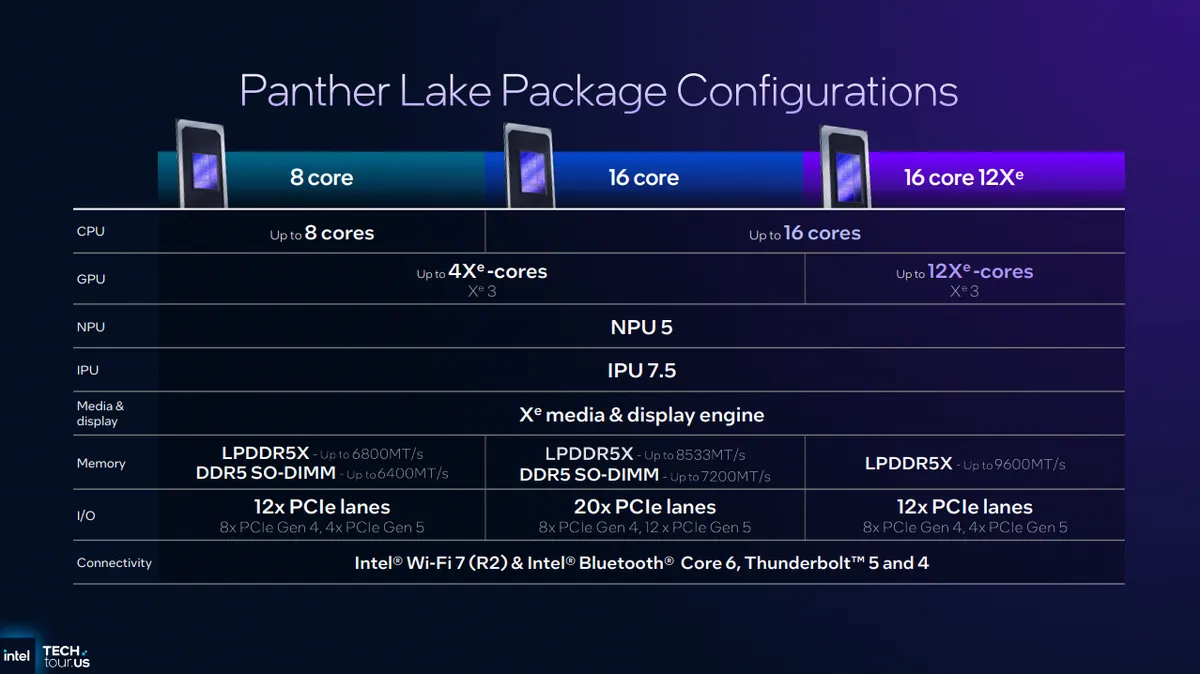

目前为止,英特尔已经创建了两种不同的 18A 计算芯片,并将其与两种不同的集成 GPU(可能还有两种不同的 I/O 模块)混合搭配,进而出现了三种不同的 Panther Lake SoC。

其中最大的 Panther Lake SoC 采用 4P+8E+4LPE CPU 核心配置,并结合了 12 Xe3 核心 GPU。它将只能使用 LPDDR5X 内存,并支持 Panther Lake 产品中最快的传输速率:9600 MT/s。

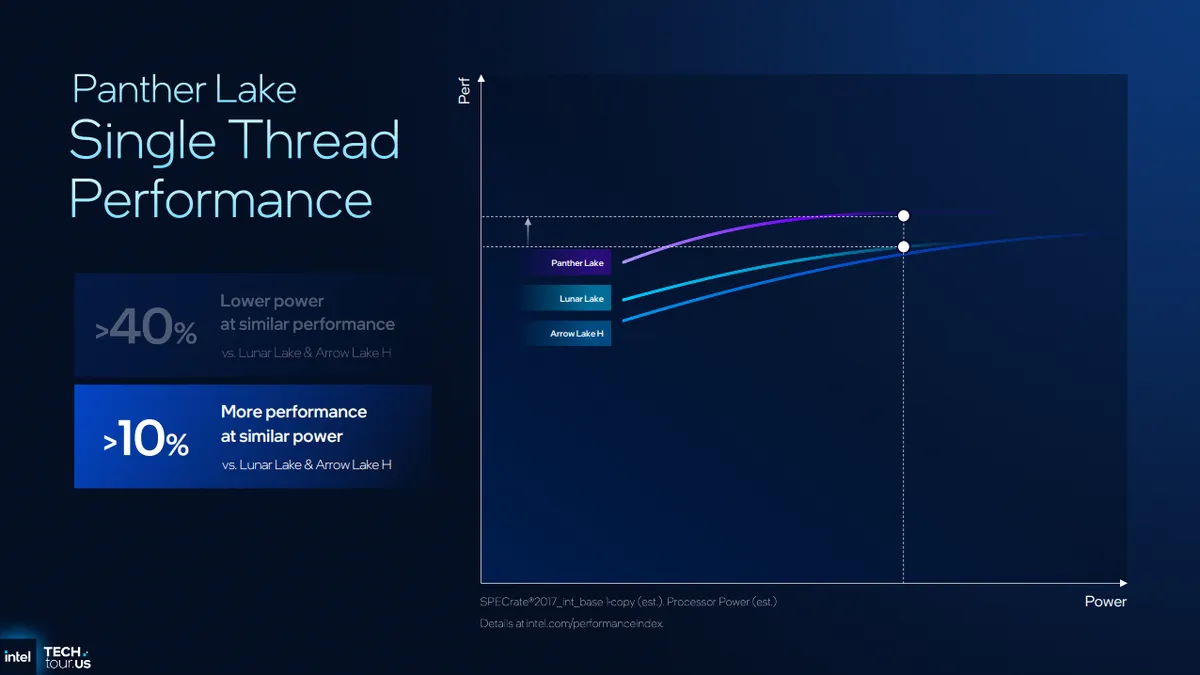

英特尔对 Cougar Cove 的单线程性能进行了高级预览,表明新的 P 核可以在与 Lunar 和 Arrow Lake 类似的功率下提供高 10% 的性能,或者在要求较低的工作负载下以类似的性能降低 40% 的功率。

在多线程性能上,英特尔表示,Panther Lake 可以在与 Lunar Lake 类似的功耗下,性能提升 50%,或者在与 Arrow Lake-H 类似的多线程性能下,功耗降低 30%。